# BI-POLAR IC'S FOR MICROWAVE SIGNAL PROCESSING

Dr. Carl Ryan

Motorola Inc.

Scottsdale, Arizona

## ABSTRACT

Various microwave signal processing functions can be performed with monolithic circuits designed to operate as high speed logic elements. The ease of interfacing with these circuits for various modes of operation offers a significant advantage over more conventional microwave components. The application of the one GB/S logic family is demonstrated by a 2 GHz prescaler, a QPSK Modulator, a QPSK Demodulator and an Adaptive Equalizer.

### 1. Introduction

Applications of monolithic integrated circuits to the low microwave end of the frequency spectrum is becoming more popular. These circuits have progressed to the point where sophisticated signal processing can be achieved with a minimum use of discrete parts.

Several signal processing applications will be presented in this paper. The set of monolithic circuits used for these applications was designed as a high data rate digital logic family which consists of three basic functions. These are the flip flop, gate, and Exclusive OR. Applications of these circuits in a modulator, demodulator, and a frequency synthesizer is presented.

### 2. Circuit Characteristics

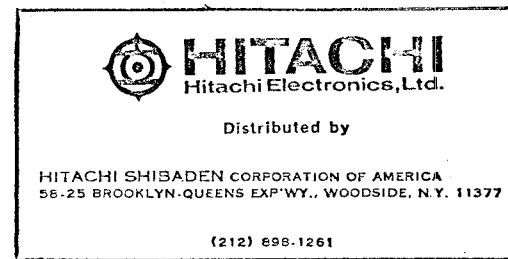

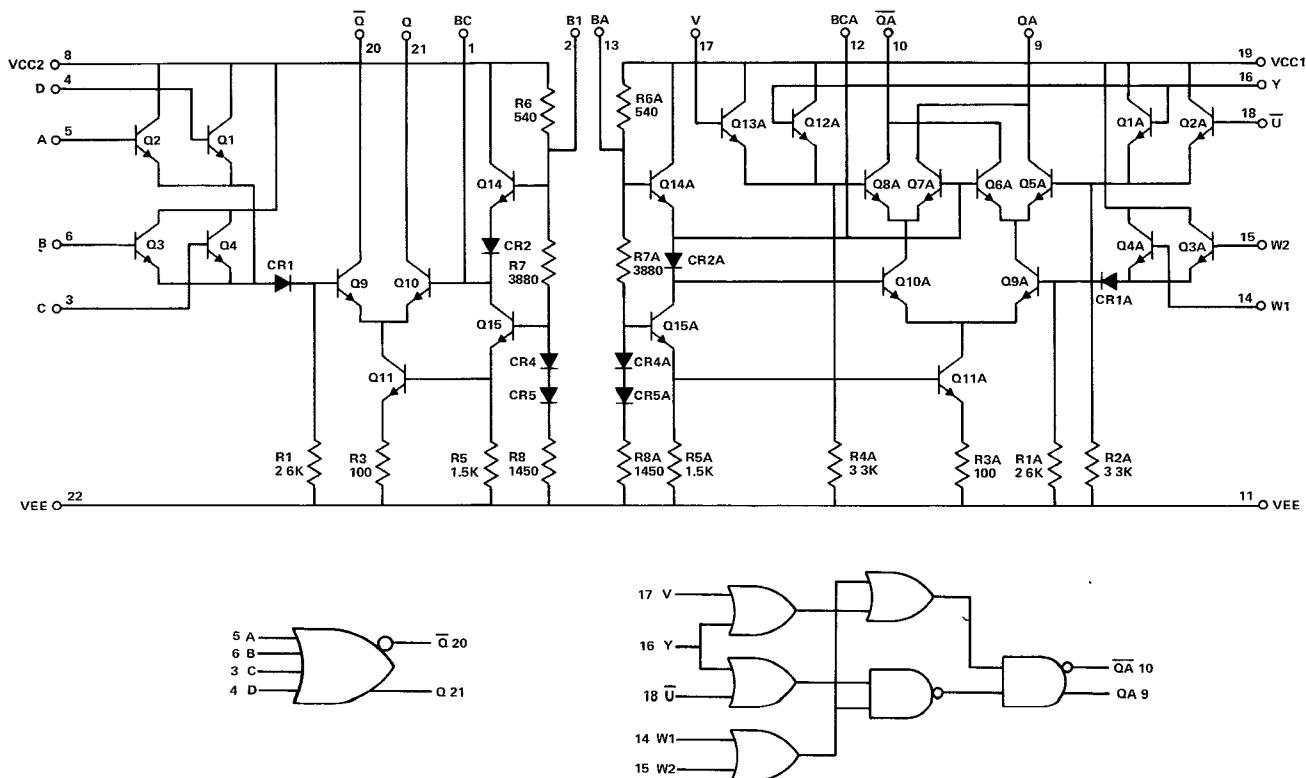

Three basic digital functions are provided in the high speed digital circuit family. These are the flip flop, 4 input OR/NOR gate and the Exclusive OR/Signal Switch. These circuits are designed to process digital data up to 1 GB/S and makes use of a form of emitter coupled logic with the outputs connected as open collectors instead of the more conventional emitter follower outputs. Figure 1 and Figure 2 are schematics of the circuits.

These circuits have a propagation delay of approximately .5 nanosecond and an output rise time of less than .4 nanoseconds in a 68 ohm load impedance. When used to process analog or a combination of analog and digital signals additional performance characteristics are necessary such as input/output isolation, small signal bandwidth and terminal impedances. These parameters will be discussed in subsequent sections to demonstrate the various applications of the circuits to microwave signal processing.

### 3. Frequency Synthesizer Prescaler

One of the more classical applications of a high speed flip flop is for use as a prescaler in frequency synthesizer application. These prescalers normally perform the divide by two or divide by four function.

Both the divide by 2 and divide by 4 have been implemented with the logic circuits to obtain a maximum input frequency of 2 GHz. The divide by four is implemented with a single flip flop and a delay line in the feedback path. This procedure results in a reduced operating bandwidth over the conventional ring divide by four, however, the simplification of the clock drive (2 GHz) and reduced circuit count is important in many applications.

### 4. QPSK Modulator

A serial QPSK Modulator can be easily implemented with the high speed logic circuits. The first modulation step is accomplished with a  $0^\circ$  or  $90^\circ$  switching operation. The single-pole double-throw switching operation of the circuit is used to switch one of the two output ports of a  $90^\circ$  hybrid. The phase balance of the two input ports of the logic circuits is such that less than  $3^\circ$  static phase error over a  $50^\circ\text{C}$  temperature change is encountered. The switching from one state to the other is accomplished in less than .25 nanoseconds. The data rate is limited by the upper limit on the L band subcarrier which can be used in the modulator. Present design is such that this subcarrier must be limited to less than 700 MHz.

The final stage of modulation is achieved with an exclusive OR circuit. This circuit provides the  $0^\circ$  or  $180^\circ$  phase modulation with an accuracy similar to that obtained in the signal switch. The small ( $\approx .5$  dB) residual amplitude modulation obtained in the Exclusive OR circuit is removed by a gate connected as a limiter. This gate provides a small signal gain of 10 dB and a power output of -3 dBm in a 50 ohm load.

### 5. QPSK Demodulator

The use of the Exclusive OR circuits in a phase detector application has also been demonstrated with the development of a High Data Rate QPSK Demodulator.

These circuits work satisfactorily for phase detector applications where precise DC offset is not important. The demodulator design was configured such that the approximately 10% DC offset was eliminated by constraining the input data to be a 50% duty factor signal and thus capacity coupling the phase detector output to the Costas type of phase locked loop. Operation up to 500 MB/S data rate has been demonstrated with this technique.

## 6. QPSK Adaptive Equalizer

The design of High Data Rate QPSK systems is such that channel and hardware equalization can be accomplished at either a microwave frequency (typically C band) or at baseband. The use of the exclusive OR circuit as a five-quadrant multiplier to form the active elements of a transversal filter results in a base band equivalent to the band pass equalizer. The additional advantage of operating on the base band signals is that the filter can be configured to be fully adaptive with only limited additional components.

A 5 section adaptive equalizer has been constructed by using these monolithic integrated circuits and is capable of operating at greater than a 400 MB/S data rate.<sup>1</sup>

## 7. Conclusions

Various microwave signal processing functions can be performed with monolithic circuits which have been designed to operate as high speed logic elements. The ease of interfacing with these circuits for various modes of operation offers a significant advantage over more conventional microwave components.

The use of these circuits provides an important alternative to the system design, i.e., processing the signals at base band or microwave frequencies.

<sup>1</sup> C. Ryan, Jim Stilwell, "Performance of A 5 Section Adaptive Equalizer for a 350 MB/S QPSK Modem". EASTCON 1974.

FIGURE 1. EXCLUSIVE OR AND FOUR INPUT GATE

FIGURE 2. DUAL FLIP FLOP